在計算機科學領域,軟件開發與計算機組成原理常被視為兩個相對獨立的領域:一個偏重邏輯與抽象,一個偏重硬件與底層。深入理解計算機組成原理,特別是其核心的“組成篇”,對于軟件開發工程師而言,是突破性能瓶頸、編寫高效可靠代碼、乃至構建卓越系統的關鍵。這不僅是知識的補充,更是一種思維模式的升維。

一、 橋梁:高級語言與機器世界的對話

軟件開發始于高級編程語言,但最終所有邏輯都必須轉化為處理器能夠識別和執行的微操作。理解計算機組成,就是理解這場“對話”的翻譯過程。

- 指令集架構(ISA):這是軟件與硬件的契約。無論是x86、ARM還是RISC-V,ISA定義了處理器能理解的基本指令(如加、減、跳轉、訪存)。編譯器的工作就是將C++、Java、Python等高級代碼編譯成符合目標ISA的機器碼。了解ISA,能幫助開發者理解不同平臺性能差異、優化關鍵循環,甚至進行底層性能調優(如利用特定指令集擴展)。

- 內存層次結構:從寄存器、高速緩存(Cache)、主存(RAM)到磁盤,訪問速度與容量成反比。不了解Cache的運作原理(如緩存行、命中率、局部性原理),很可能寫出導致大量“緩存未命中”的代碼,即便算法時間復雜度最優,實際運行也可能異常緩慢。例如,遍歷二維數組時,按行訪問與按列訪問在性能上可能有天壤之別。

二、 核心:CPU如何驅動你的代碼

中央處理器(CPU)是計算機的“大腦”,其組成與工作方式直接決定了軟件的執行效率。

- 運算器與控制器:這是CPU的核心。運算器執行算術邏輯運算,控制器則根據指令指揮全機。理解其工作流程(取指、譯碼、執行、訪存、寫回),能讓開發者對程序執行的微觀時間線有清晰概念。

- 流水線與并行:現代CPU普遍采用指令流水線技術,像工廠流水線一樣同時處理多條指令的不同階段。分支預測失敗、數據冒險等問題會導致流水線“冒泡”停頓。編寫代碼時(如優化if-else邏輯、減少條件分支),有意識地輔助CPU進行更準確的分支預測,能顯著提升性能。

- 多核與并發:理解CPU的多核架構、緩存一致性協議(如MESI),是進行高效多線程編程的基礎。這能幫助開發者規避偽共享等問題,設計出真正能利用多核優勢的并發數據結構與算法。

三、 瓶頸:跨越存儲與I/O的鴻溝

馮·諾依曼體系結構的“存儲程序”思想,使得存儲器成為關鍵一環。軟件開發必須直面存儲系統的特性。

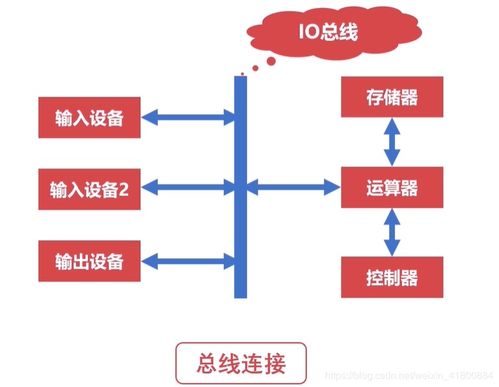

- 主存與總線:內存的尋址方式、總線帶寬和時序,影響了數據搬運的速度。對于需要處理海量數據的應用(如數據分析、圖形處理),優化內存訪問模式與數據對齊,有時比優化計算本身更重要。

- 輸入/輸出系統:I/O操作(磁盤、網絡)相比CPU運算慢數個數量級。理解I/O控制器、中斷、DMA(直接內存存取)機制,能幫助開發者設計出高響應的異步I/O模型,避免線程阻塞,這也是現代高并發服務器(如Nginx、Redis)的核心設計思想之一。

四、 實踐:將組成原理思維融入開發

- 性能分析與調優:當使用性能分析工具(如Perf、VTune)發現“CPI高”或“L3緩存未命中率高”時,組成原理知識能讓你快速定位到是算法問題、數據結構布局問題,還是訪存模式問題。

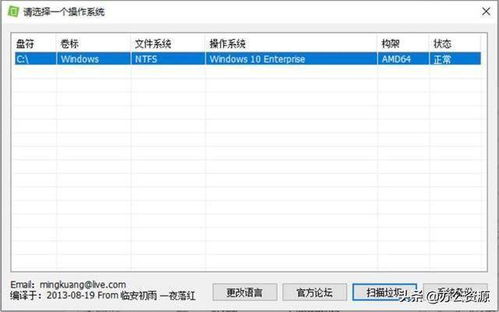

- 系統級編程:開發操作系統、數據庫、游戲引擎、編譯器等領域,必須深入與硬件交互。理解中斷、內存管理單元、虛擬地址與物理地址轉換、設備驅動等概念,是不可或缺的。

- 問題診斷與調試:某些棘手的Bug,如由內存對齊引起的崩潰、多線程下的極難復現的數據錯誤,其根源往往在硬件層面。組成原理知識提供了探查這些“幽靈”問題的線索和工具。

- 前瞻性設計:了解硬件發展趨勢(如存算一體、異構計算、新型非易失存儲器),有助于在軟件架構設計上提前布局,搶占技術先機。

###

對于軟件開發者而言,計算機組成原理并非遙不可及的硬件知識,而是隱藏在高級抽象之下的運行真相。掌握它,意味著你不僅能告訴計算機“做什么”,更能深刻理解它“如何做”,從而在資源(時間、空間、能耗)的約束下,找到最優解。從寫出可運行的代碼,到寫出能極致發揮硬件潛能的代碼,這中間的飛躍,正是“搞定”組成原理所帶來的核心價值。它讓開發者從程序的“編劇”,成長為駕馭整個計算機系統的“導演”。